MIPI規格是什麼?

MIPI行動產業處理器介面 (英文全名為Mobile Industry Processor Interface,簡稱MIPI), 是由MIPI聯盟針對移動設備(如:智慧型手機、平板電腦、筆記型電腦和混合裝置等各種行動裝置)的處理器設計所定義的規範,隨著5G、人工智慧、物聯網等技術日漸成熟,相關處理器及裝置需求也越來越高,MIPI規範成為重要角色。

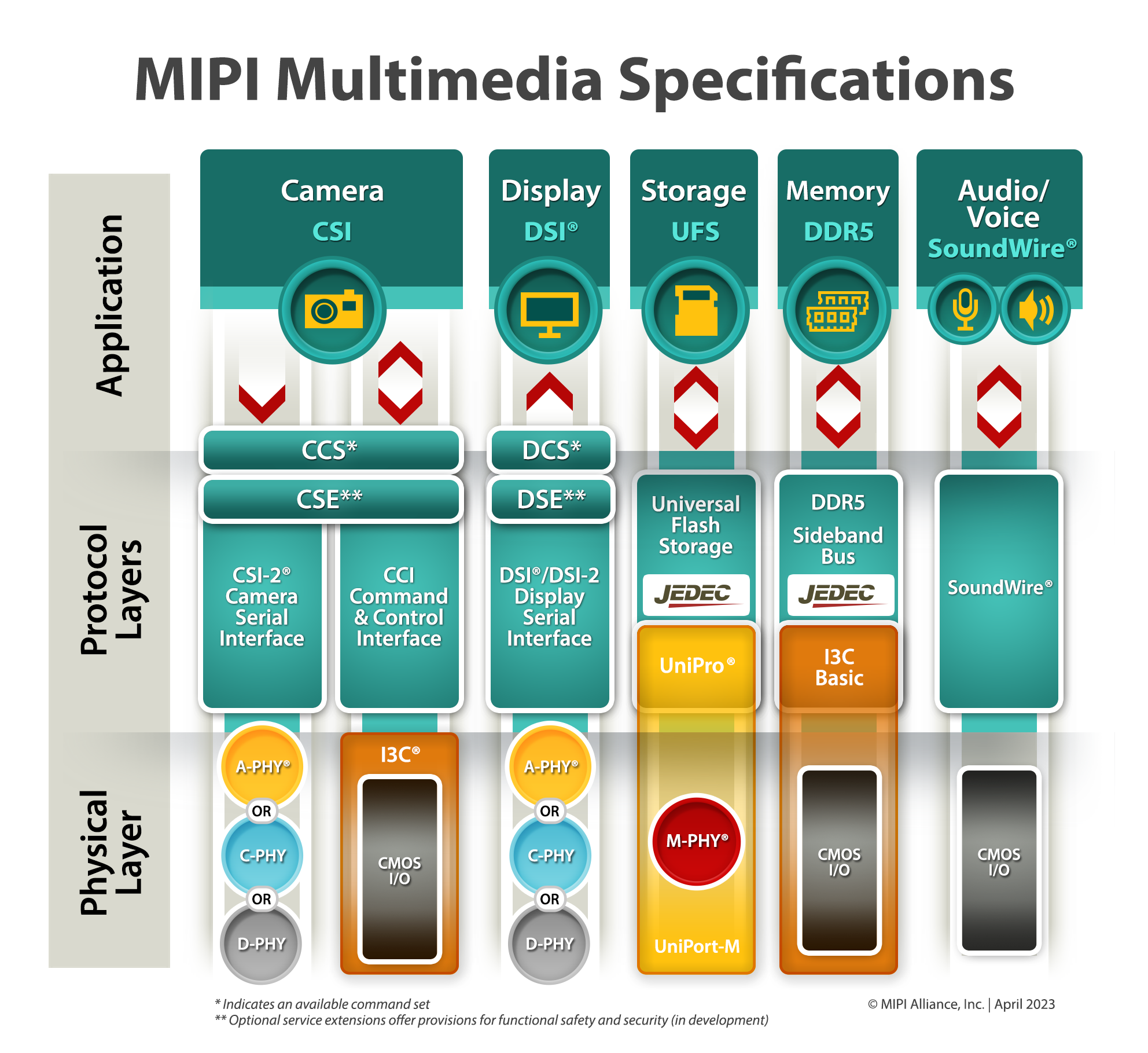

MIPI規範共有六種類型的介面,其中MIPI規範中的多媒體(Multimedia)類別,如下圖所示,主要分為三個層面:

◆ 應用層(Application Layer)

◆ 協定層(Protocol Layer)

◆ 實體層(PHY Layer)

而MIPI主要應用類型可分為Camera (CSI)、Display (DSI)、Storage(UFS)。

如同多數的技術介面,MIPI聯盟也有制定一份標準測試文件來明確定義測試條件、方法與項目,MIPI的測試文件稱為規格一致性測試(CTS/Conformance Test Suit)文件,通過一致性測試可以有效減少影像攝影畫面雜訊/模糊/失真、影像延遲等問題。

和一般認證測試不同的是廠商可參照測試文件指引自行執行一致性測試,可不用透過協會認可的第三方認證實驗室執行測試。若要執行此測試,必須先備齊相關測試設備及環境,然而根據百佳泰多年測試經驗,多數廠商碰到最大的問題是並不是在這部分,而是沒有足夠的測試經驗。由於MIPI多用於移動設備內部,必須透過焊接或是探針直接連接方式進行量測,因此相較於一般常見的USB、HDMI等外接介面,量測困難度增加許多。

接下來我們將以常見的D-PHY/C-PHY為例分享產品在測試時常遇到的問題。

MIPI D-PHY是什麼?

MIPI D-PHY是一種結合高速、低功耗的訊號傳輸模式,主要應用於Camera (CSI)、Display (DSI)。

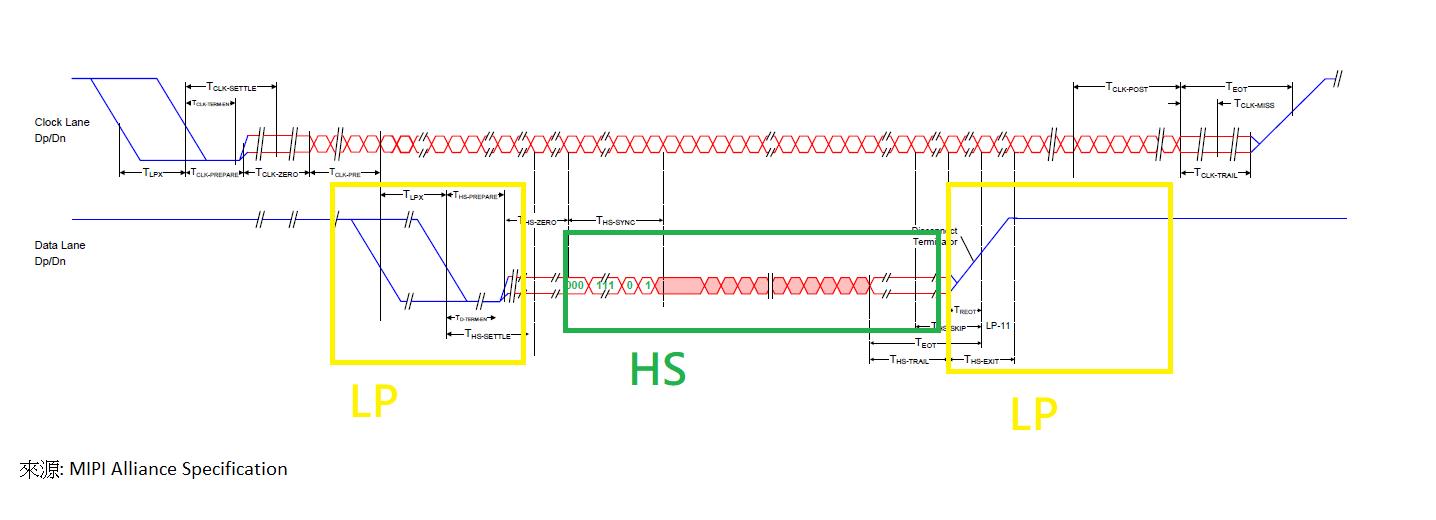

訊號組合1對Clock差分訊號以及1~4對Data差分訊號,支援HS mode (High Speed)和LP mode (Low Power) 模式之間切換。

Transmitter( TX)測試的要求與方法

由於智慧型手機、平板電腦、車機上的鏡頭介面跟影像顯示介面都已是成品的階段,如同前面所提到的,若要進行訊號測試就只能透過焊接或是探針直接連接方式進行量測。

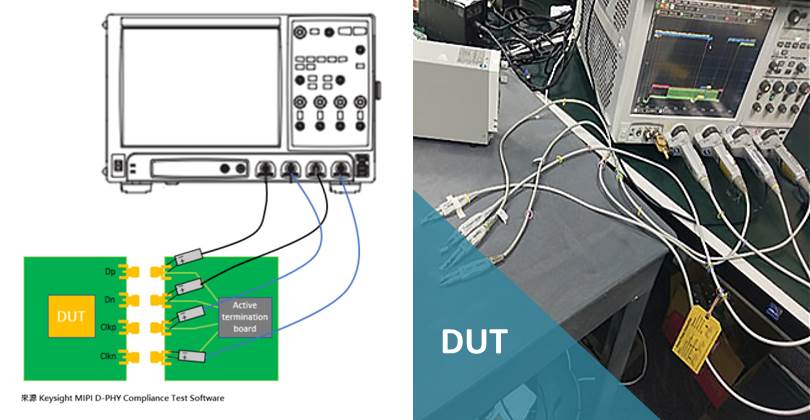

下圖是測試環境的連接示意圖:

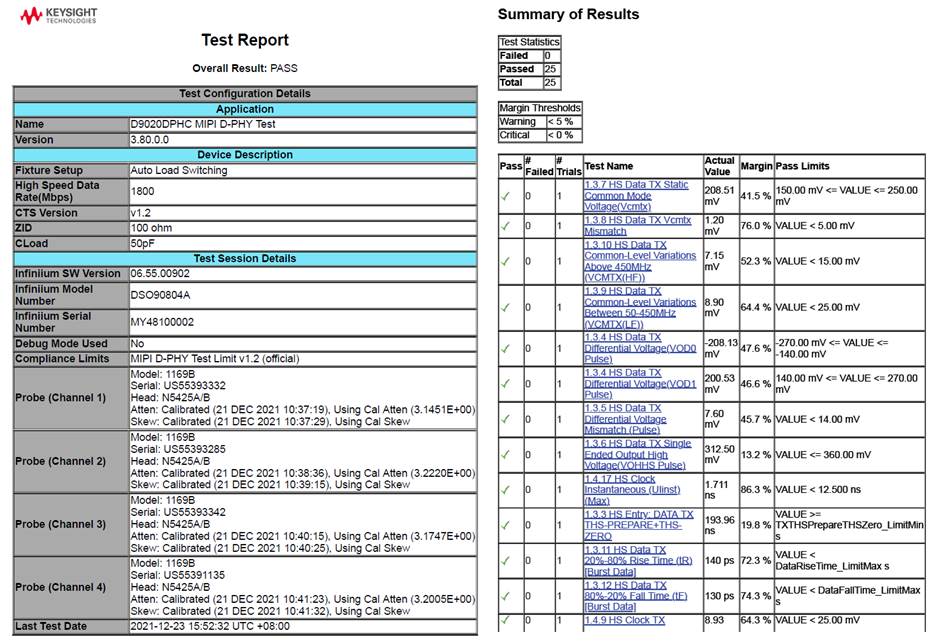

測試設備是使用Keysight D9020DPHC及相符性測試軟體,針對MIPI D-PHY v2.1第9節以下及C-PHY CTS V2.1第1節以下的規格進行完整測試。

主要測項如下:

◈ High Speed Data/Clock TX

◈ Low Power Data/Clock TX

◈ Data/Clock Transmitter(HS Entry、HS Exit)

◈ High Speed Data-Clock Timing

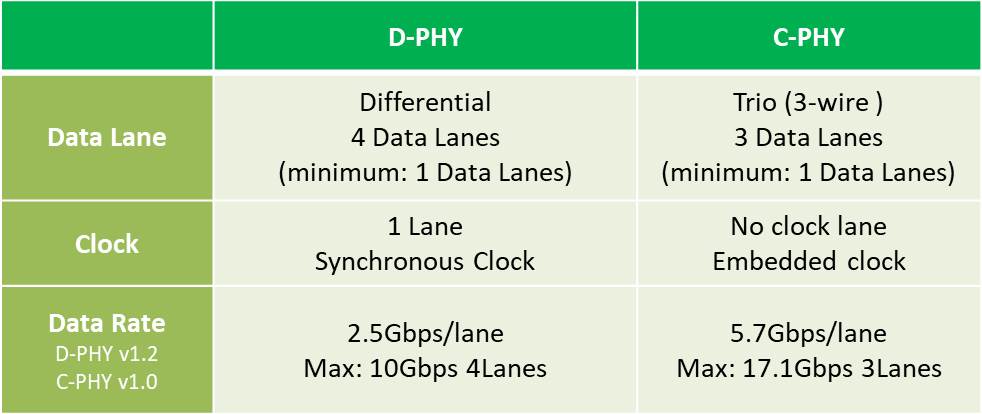

MIPI C-PHY

與D-PHY相同,結合高速、低功耗的訊號傳輸模式,應用於(CSI、DSI)。兩者主要差異點如下:

Transmitter (TX)測試的要求與方法

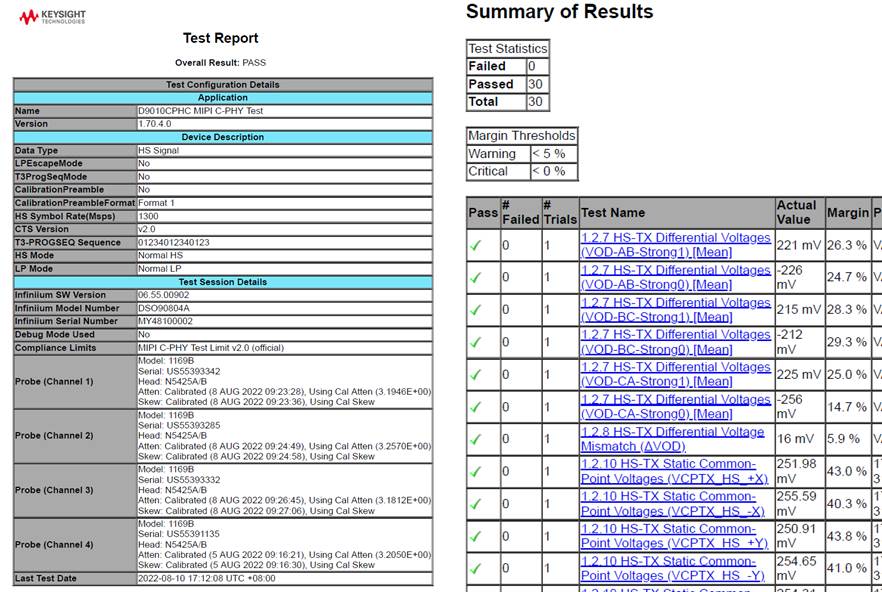

測試設備是使用Keysight D9010CPHC MIPI C-PHY Compliance Test Software,可針對MIPI C-PHY v1.2第9節和C-PHY CTS v1.1第1節的規格進行完整測試。

主要測項如下:

◈ High-Speed Transmitter (HS-TX) Electrical Tests

◈ Global Timing Tests(T3-Prepare、HS Exit)

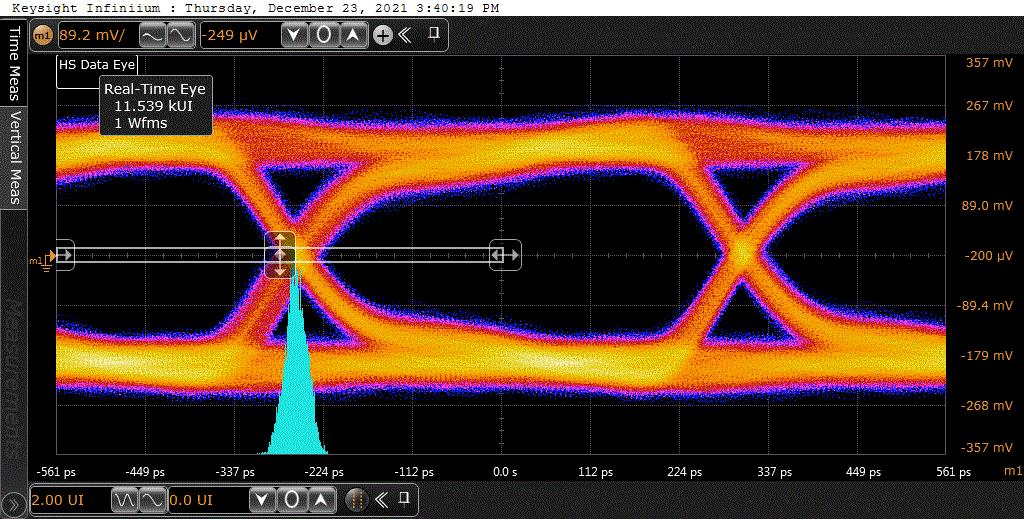

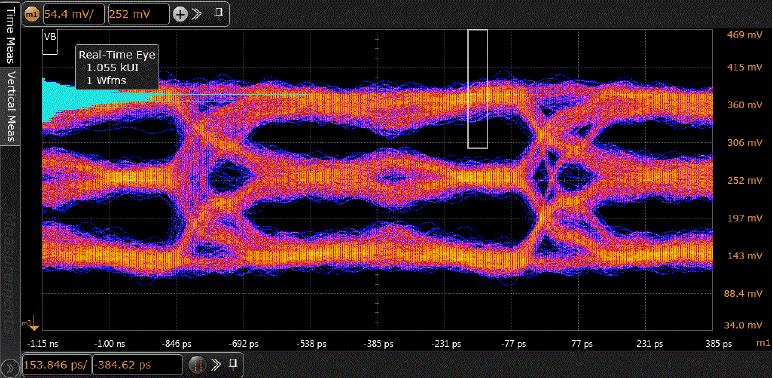

上圖擷取不同模式,進行訊號的示意圖

案例分享

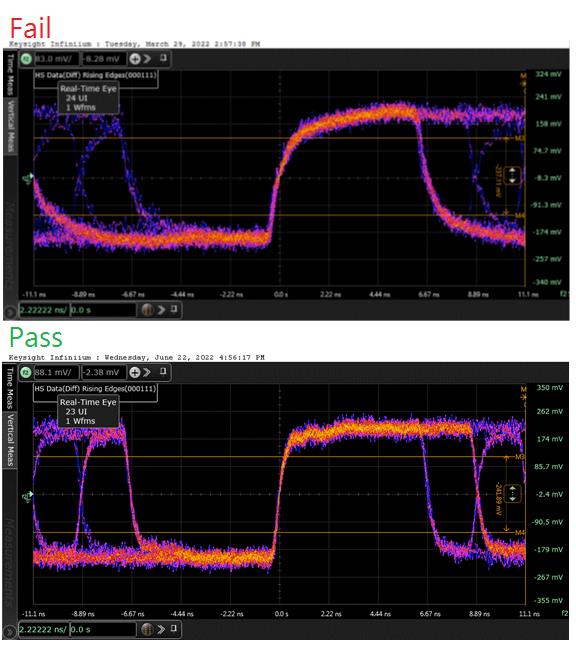

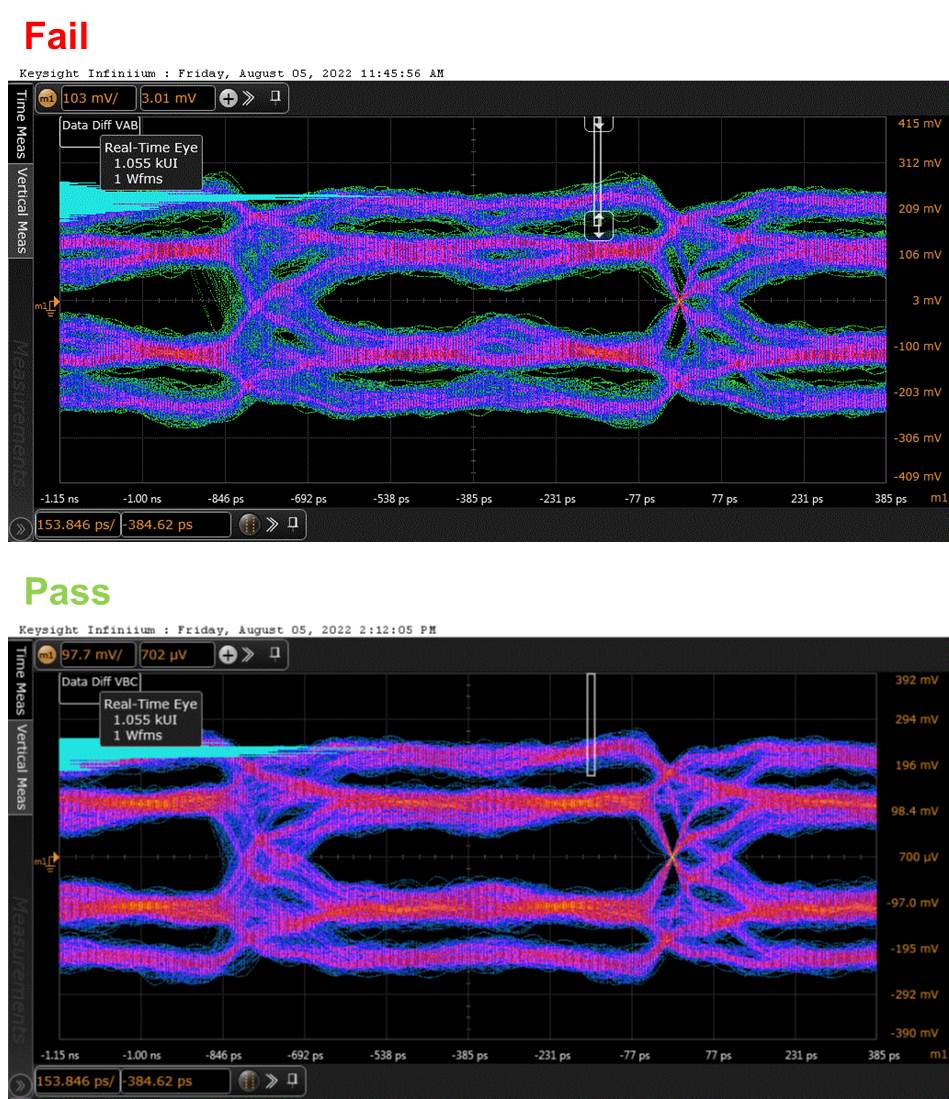

1. 量測位置影響測試品質

MIPI D-PHY/C-PHY TX主要規範是量測晶片輸出端。

如測試點位位置過遠,那麼就會影響訊號的衰減,且當driver能力不夠時會造成rise/fall爬升能力不夠,導致over spec、品質訊號較差。

D-PHY

C-PHY

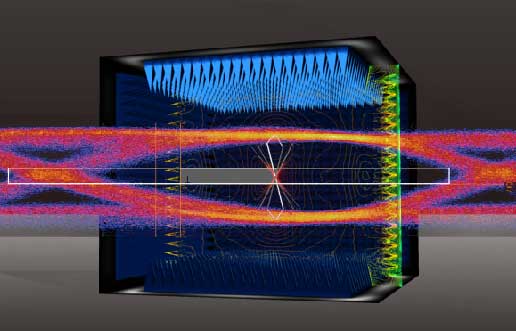

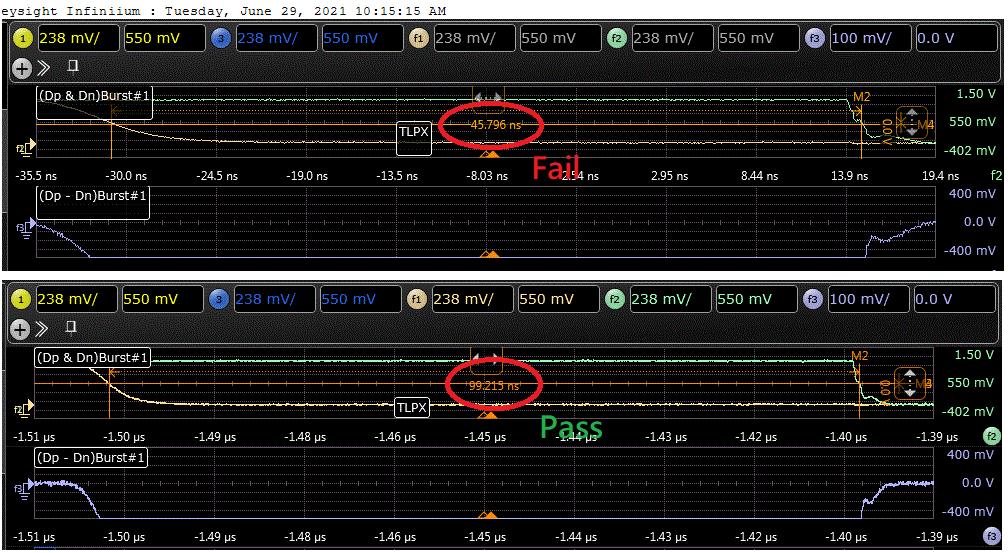

2. 晶片timing參數設定調整有誤導致測試Fail

因晶片timing參數設定問題,導致Data/Clock Transmitter(HS Entry、HS Exit) timing fail。百佳泰建議Timing skew fail可透過晶片商提供修改參數來調整。

如下圖可見當數值低於50,則會導致over spec; 反之,如數值高於50,數據結果會出現Pass。

百佳泰測試實驗室

百佳泰建置了完整的方案,可協助客戶根據MIPI標準測試關鍵量測參數,以確保客戶的裝置擁有出色的效能,同時百佳泰還擁有相關設備可提供各種訊號完整性測試能力,例如DDR, UFS, Ethernet…等,如有任何需求,歡迎您與我們聯繫:service@allion.com,或者填寫表單聯繫百佳泰!百佳泰將為您打造專屬測試服務!

成功案例